This article was originally published on November 7, 2022.

Editor’s Note: This content is contributed by Romisaa Samhoud, Product Marketing Manager for Cost-Optimized FPGAs

Building on the success of the AMD Zynq™ UltraScale+™ MPSoCs and AMD Artix™ UltraScale+ FPGAs, AMD is extending the UltraScale+ family with two new devices.

The new AU7P and ZU3T devices are based on the 16 nm FinFET process for low power, high performance-per-watt, and small form factor applications. These small, low cost, and low power entry points to the programmable logic (PL) transceiver-based UltraScale+ family offer improved features such as high IO-to-logic density, UltraRAM, DSP, etc.

The New Artix UltraScale+ AU7P FPGA

The AU7P device is the lowest density, lowest power, and most cost-optimized 12.5 Gbps transceiver-based FPGA in the Artix UltraScale+ portfolio. It offers high I/O-to-logic ratio and high memory-to-logic ratio for storing and buffering large amounts of data for processing and compute applications.

The new device provides up to 50% lower static power, 20% more I/O-to-logic ratio, and twice as many 3.3 V HDIO compared to the AU10P device.

New Zynq UltraScale+ ZU3T MPSoC

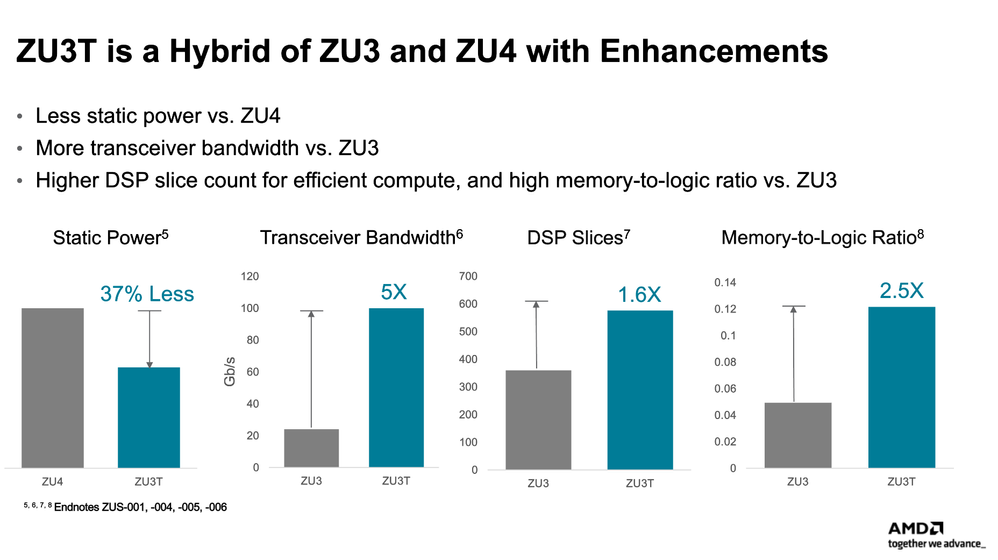

The ZU3T MPSoC is the smallest device added to the Zynq UltraScale+ family with 12.5 Gbps GTH transceivers for cost-optimized applications. The GTH transceivers are highly configurable and tightly integrated with programmable logic resources of the UltraScale+ architecture. The ZU3T device also has 5X the transceiver bandwidth compared to the ZU3 device for critical networking applications, vision and video processing, and secured connectivity.

The new device has higher DSP slice count compared to ZU3 device for better signal processing compute. The additional UltraRAM adds 2.5X the embedded memory for embedded and video processing applications.

As part of the Zynq MPSoC family, the ZU3T device contains a 64-bit processor combining real-time control with soft and hard engines for graphics processing. The integration of both an Arm®-based CPU sub-system for advanced analytics and on-chip programmable logic for task acceleration creates new possibilities for optimizing a broad range of applications, including smart cities, camera monitors, medical imaging, and automotive infotainment.

The AU7P device is expected to begin shipping pre-production and production silicon in the second half of 2023.The ZU3T device is expected to begin shipping pre-production silicon to early access customers in the first half of 2023, with production silicon expected in the second half of 2023.

AU7P and ZU3T devices will be available in automotive (XA) grade, qualified according to AEC-Q100 test specifications with full ISO26262 ASIL-C level certification. This scalable solution is ideally suited for various automotive customer platforms by delivering the right performance/watt while integrating critical functional safety and security features.

Visit our webpage to learn more about our UltraScale+ Cost-Optimized FPGAs and SoCs. Contact your local sales representative or visit our contact sales form to inquire about device pricing and schedules.

Endnotes:

1. AUS-001. Static Power calculation based on scaling of the AU10P as an estimate of AU7P static power on Xilinx Power Estimator (XPE) tool version 2022.1.2, as of October 24, 2022. Power scaled based on logic cell count difference compared to AU7P. Actual static power may vary with actual part specifications.

2. AUS-004: Calculated based on published Artix UltraScale+ specifications using HDIO. AU7P has 144 HDIO while AU10P has 72 HDIO.

3. AUS-005: Calculated based on published Artix UltraScale+ specifications using total IO (HD + HP). AU7P has 248 max total IO while AU10P has 228 max total IO.

4. AUS-006: Calculated based on published Artix UltraScale+ specifications using total Block RAM (BRAM). AU7P has 3.8 Mb BRAM while AU10P has 3.5 Mb BRAM.

5. ZUS-001: Static power calculated based on scaling of the ZU4 as an estimate of ZU3T static power on Xilinx Power Estimator (XPE) tool version 2022.1.2, as of October 24, 2022. Power scaled based on logic cell count difference compared to ZU3T. Actual static power may vary with actual part specifications.

6. ZUS-004: Based on published Zynq UltraScale+ specifications. ZU3 has a total of 24 Gbps of bandwidth (4 PS-GTR @ 6Gb/s) while ZU3T has a total of 124 Gbps (4 PS-GTR @ 6 Gbps + 8 GTH @ 12.5 Gbps).

7. ZUS-005: Based on published Zynq UltraScale+ specifications. ZU3 has 360 DSP slices while ZU3T has 576 DSP slices.

8. ZUS-006: Calculations based on published Zynq UltraScale+ specifications using total block RAM (BRAM) + UltraRAM when available. The total BRAM and UltraRAM is 7.6 Mb for ZU3 and 17.1 Mb for ZU3T.