This article was originally published on Jun 15, 2020.

Editor’s Note: This content is contributed by George Wang, Product Marketing Manager for AI & AI Engines.

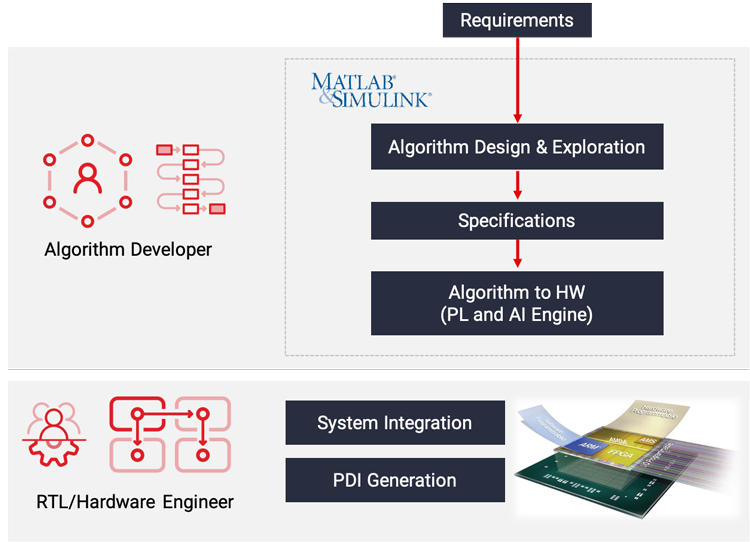

Xilinx Add-on for MATLAB & Simulink is a single tool that unifies Model Composer and System Generator for DSP. It is a Model-Based Design tool enabling algorithm and RTL/hardware developers to rapidly design and explore within the MathWorks Simulink® environment and target Xilinx devices.

The tool provides high-level performance-optimized blocks and validates functional correctness through system-level simulations. It also transforms algorithmic specifications to production-quality implementation and accelerates the path to production through automatic code generation.

Add-on for MATLAB & Simulink covers Programmable Logic (PL) and AI Engine domains. For PL domain, you can use either RTL based blocks (cycle accurate) or High Level Synthesis (HLS) based blocks.

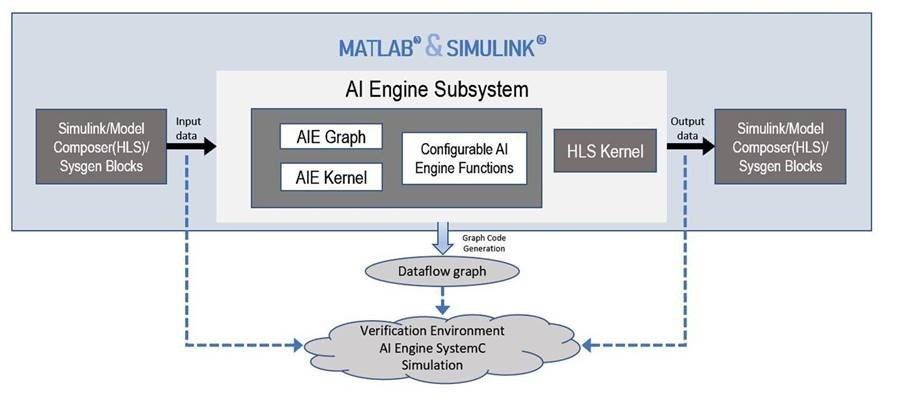

In the 2020.2 release, the Add-on for MATLAB & Simulink supports Xilinx Versal™ platforms. It enables the rapid simulation, exploration, and code generation of algorithms targeted for AI Engines within the Simulink® environment. User can achieve this by:

- Importing AI Engines kernels and data-flow graphs as blocks.

- Controlling the behavior of the kernels and graphs by configuring block mask parameters.

- Adding Configurable AI Engine functions from the available AI Engine DSP Library blocks.

Simulation results can be visualized by seamlessly connecting Simulink sink blocks such as scope, display, and spectrum analyzer to any signal with the design. This will make analyzing and debugging the model significantly simpler. Furthermore, the simulation results can be sent to the MATLAB® workspace for in-depth analysis.

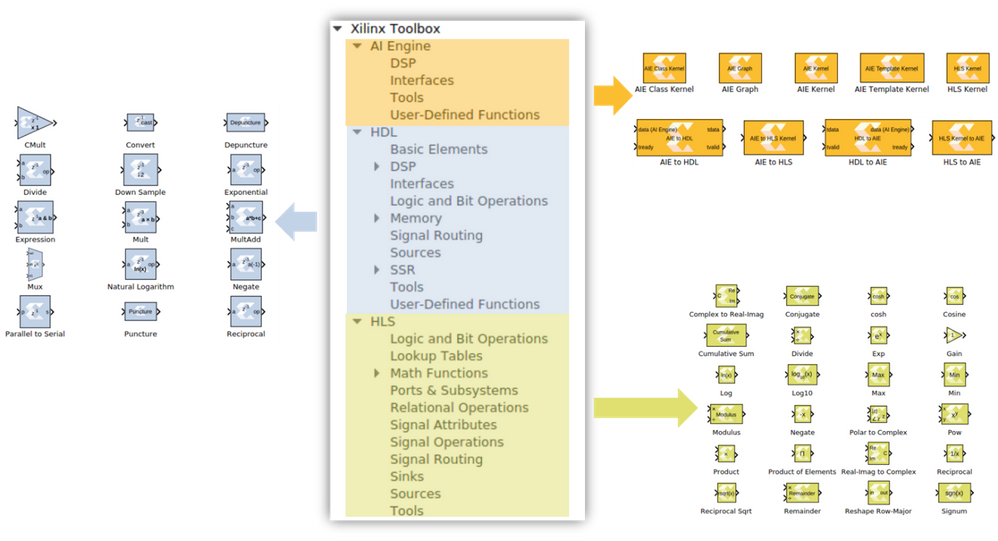

Add-on for MATLAB & Simulink provides a set of AI Engine library blocks for use within the Simulink environment. These include:

- Blocks to import kernels and graphs which can be targeted to the AI Engine of Versal devices.

- Blocks to import HLS kernels which can be targeted to the PL portion of Versal devices.

- Blocks that support the connection between the AI Engine and the Xilinx HDL blockset.

- Configurable AI Engine functions.

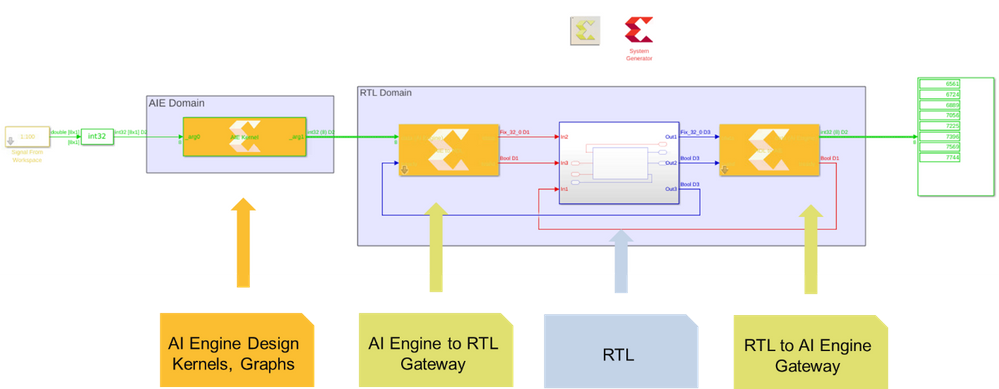

Connecting HLS kernel blocks, HDL library blocks, and AI Engine blocks allow modeling and simulation of the heterogeneous platforms which can be targeted to both programmable logic and AI Engines on Versal™ Platforms. The functional simulation will run significantly faster than a cycle-accurate simulation allowing rapid iteration of the design.

In addition to functional simulation, users can also use the Add-on for MATLAB & Simulink Hub to generate dataflow graphs and a test bench. Moreover, the tool can optimally execute the test bench to ensure the output of the cycle-accurate System C simulator of the generated graph code matching the results of the reference design in Simulink environment, saving the end user a significant amount of time

A typical AI Engine design flow is shown in the following diagram.

Add-on for MATLAB & Simulink enables mixed domain design for Versal Platforms:

Download the Add-on for MATLAB & Simulink here

For more details about the AI Engine flow, please check (UG1498) and (UG1483).