What’s New in the Vitis HLS Tool 2022.2

- Subscribe to RSS Feed

- Bookmark

- Subscribe

- Printer Friendly Page

- Report Inappropriate Content

This article was originally published on November 21, 2022.

Editor’s Note: This content is contributed by Sriranjani Ramasubramanian, Product Marketing Manager for Vitis HLS.

The new Vitis™ HLS tool 2022.2 release offers feature improvements and enhancements to the tool set.

Coding Style Enhancement to boost Performance

Vitis HLS provides pragmas that can be used to help optimize the design and improve throughput performance. The PERFORMANCE pragmas apply to loops and loop nests in order to determine the performance.

Performance pragmas can now automatically infer lower-level optimizations, such as unroll, pipeline, array_partition, and inline pragmas. The ability to specify throughput requirements at the loop level reduces complexity as users do not have to figure out partitioning, pipelining and unrolling needs, thus making the HLS tool easier to use.

With the 2022.2 enhancement, users can specify a high-level constraint (target_ti) to specify the number of clock cycles between the successive start of a loop.

For example, for an image processing function that processes a single frame per invocation with a throughout goal of 60fps, the target throughput for the function would be 60 invocations per second. If the clock frequency is 180 MHz, then the target_ti is 180M/60 (i.e., 3 million clock cycles per function invocation). The Vitis HLS tool will then try to achieve this specified performance target in the design.

Users can use the following syntax to place the pragma in the code

set_directive_oerfirnance <label> -target_ti=<value>

#pragma HLS performance target_ti=<value>

-target_ti=<value>: Specifies a target transaction interval defined as the number of clock cycles to execute all the iterations of the loop, until the loop can start from the first iteration again

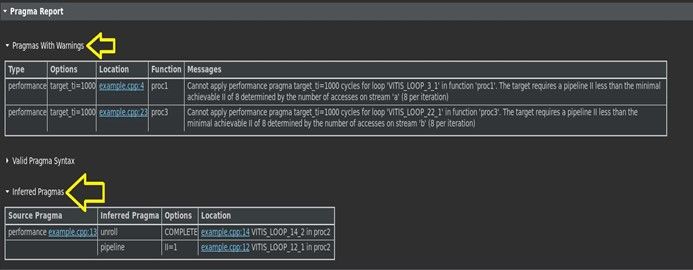

The User Pragma Report shown below will now include the specified target_ti and enable the user to quickly identify any design pragma issues.

Trace value of variables after synthesis to help with debugging

It is a common practice to insert printf statement for debugging purposes in the C-code. The hls::print function is similar to the printf in C in that it prints strings or arguments to a standard output.

This new feature will print strings or arguments not only to a standard output but also to the simulation log during C simulation, RTL co-simulation, and emulation in the Vitis IDE.

This function is helpful for debugging—for example, tracing the values of variables or tracing the order in which code blocks are executed across complex control and concurrent execution.

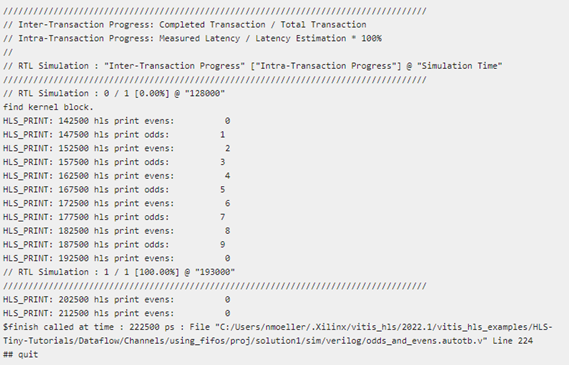

In the example shown below, the value of “i” is printed at each iteration of the loop in both C simulation and RTL co-simulation.

#includ "hls_print.h"

...

for (int i=0; i<N; i++) {

#pragma HLS pipeline ii=1

hls::print ("looop %d\n", i);

...

Example of a log file with the new hls::print statements.

Streaming interface Support for FFT and FIR IPs

It is common practice for users to instantiate LogiCORE™ blocks such as FFTs and FIRs into an HLS design. FFT and FIR IP blocks have streaming interfaces with two input streams and one output stream.

In the past, these were modeled using default block control protocol ap_ctrl_chain blocks that required many layers of wrappers. Interfaces were complicated to implement, and performance was therefore impacted.

With the 2022.2 software release, users can now define a new overload of the fft() and fir() Vivado™ IP functions in the HLS header as shown below.

template <typename PARAM_T>

void fft (hls::stream<comple <float or ap_fixed>> &xn_s,

hls::stream<comple <float or ap_fixed>> &xk_s,

hls::stream<ip_fft::status_t<CONFIG_T>> &status_s,

hls::stream<ip_fft::config_t<CONFIG_T>> &config_s);

All inputs and outputs are supplied to the function as hls::stream<>, and all the ports of an FFT/FIR block will be implemented as AXI4-Stream ports.