The Xilinx Alveo SN1000: A Programmable, Composable, Portable SmartNIC Architecture

- Subscribe to RSS Feed

- Bookmark

- Subscribe

- Printer Friendly Page

- Report Inappropriate Content

This article was published on February 24th, 2021.

These HPC NICs laid the groundwork for what then became Ethernet NICs with built-in kernel bypass for electronic trading in all the world's stock markets. Over time these platforms further evolved into what has become SmartNICs or Data Processing Units (DPUs). With the emergence of Hyperscalers and Cloud Service Providers (CSPs), Xilinx has identified three things that have hampered the adoption of SmartNICs:

- Programmability

- Composability

- Portability

Xilinx's approach of providing a software-defined, hardware-accelerated platform lends itself perfectly to addressing these three issues.

Programmability

Various attempts have been made over the past decade to expose a fully programmable interface to SmartNICs, but none have been overwhelmingly successful. In parallel, the industry has lacked a standardized language and proven software development and deployment environment. Several years ago, Xilinx became an active member of the P4 Language Consortium as an Industrial Contributor to develop a language to manage network packets across many types of hardware. The P4 language has rapidly taken off, and today most SmartNICs and DPUs have adopted it as their default programming language. All of the unique logic blocks in Xilinx's new SN1000 family of SmartNICs have been written in P4.

Composability

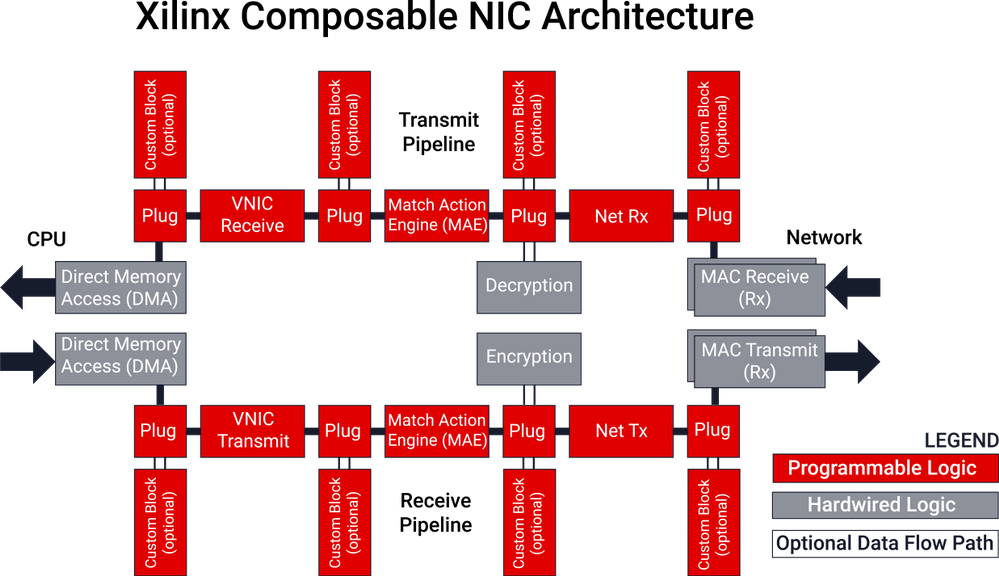

The second thing requested by Hyperscalers and CSPs is composability. This is the capability to dynamically insert new functional blocks into both the receive and transmit packet processing pipelines. These two pipelines that directly manage network packets make up the NIC's data plane. A second plane on the NIC is known as the control plane; its role is to manage the programmable blocks within the data plane. As shown above, Xilinx has leveraged our leadership in programmable logic to engineer a fully composable NIC architecture.

Both the receive and transmit pipelines that make up the data plane each have several programmable entry points where customers can attach their own blocks of code written using P4, C/C++, HDL, or HLS using our Vitis™ software development platform. Vitis then compiles this code into logic and enables the engineer to insert the block wherever they see fit in the appropriate packet processing pipeline. This allows packets to flow through the data plane at blazingly fast speeds enabling Xilinx to support wire-rate packet processing.

Other vendors who don't utilize programmable logic in their data plane must deploy large numbers of classic CPU cores, typically Arm, on their DPUs to process these network packets. This approach- using CPU cores on the DPU to process packets in the data plane- will suffer as packet rates climb into the 100s of millions of packets per second. Our software-defined, hardware accelerated approach is what will enable Xilinx's SN1000 family to outperform our competitors significantly.

Large data center customers, like Hyperscalers and CSPs, always require vendors to show their product roadmap. This roadmap demonstrates to a customer the vendor's commitment to their architecture and their plan to move that architecture forward in future generations. Often this requires that each generation is a new chip, which is an improvement over the previous chip.

Portability

Several years ago, under a partnership that eventually resulted in their acquisition by Xilinx, Solarflare began developing a fully portable SoftNIC architecture written in P4. A SoftNIC is one in which all the core NIC functions are expressed entirely as code, making the NIC easily portable between FPGA hardware platforms. The SoftNIC leverages standard hardware blocks like the Direct Memory Access (DMA) engine to talk with the host CPU, and the Media Access Control (MAC) block for Ethernet communications. These can be chip geometry specific. Also, it's often best to have the encryption block in hardware as well. Ultimately, bugs and feature additions to a SoftNIC do not require creating a new chip; customers just need to install the new bits.

The various vital components that make up the SN1000 portable NIC architecture are interfaces to the DMA engine, encryption, MAC blocks, a virtualized NIC (VNIC), and the Match Action Engine (MAE). The VNIC is how traditional OS device drivers view the NIC; it also handles checksum offloads and packet steering. The MAE in both the receive and transmit pipelines is where virtual networking requests are processed. Here Open vSwitch (OvS) functions are handled to manage traffic for virtual machines and containers running on the host. The MAE can significantly offload the host CPU from processing OS or hypervisor networking calls, sometimes returning as much as 30% of the host's CPU cycles for CSP workloads. The MAE is designed to easily interface with tc-flower and the DPDK generic flow API (rte_flow) for handling these functions. The plugin entry points, VNICs, MAEs, and NET engines are all written in software and compiled into gates. This is what Xilinx means by software-defined and hardware-accelerated.

Xilinx will be making several optional plugin modules available with the release of the SN1000 SmartNIC, and additional modules will follow in the coming months. With the SN1000, Xilinx has demonstrated the first completely composable and totally portable SmartNIC, a significant innovation in one of the most competitive sectors of our industry.