Hello, for some reason I'm getting this issue when i try to see the ILA waveforms in my design. The previous results are not fixing my issue. Does anybody know the solution?

WARNING: [Xicom 50-38] xicom: No CseXsdb register file specified for CseXsdb slave type: 0, cse driver version: 0. Slave initialization skipped.

INFO: [Labtools 27-1434] Device xc7z010 (JTAG device index = 1) is programmed with a design that has no supported debug core(s) in it.

WARNING: [Labtools 27-3361] The debug hub core was not detected.

Resolution:

1. Make sure the clock connected to the debug hub (dbg_hub) core is a free running clock and is active.

2. Make sure the BSCAN_SWITCH_USER_MASK device property in Vivado Hardware Manager reflects the user scan chain setting in the design and refresh the device. To determine the user scan chain setting in the design, open the implemented design and use 'get_property C_USER_SCAN_CHAIN [get_debug_cores dbg_hub]'.

For more details on setting the scan chain property, consult the Vivado Debug and Programming User Guide (UG908).

WARNING: [Labtools 27-3413] Dropping logic core with cellname:'u_ila_0' at location 'uuid_23E7D65A79BC59F7BC47406C1714DFAE' from probes file, since it cannot be found on the programmed device.

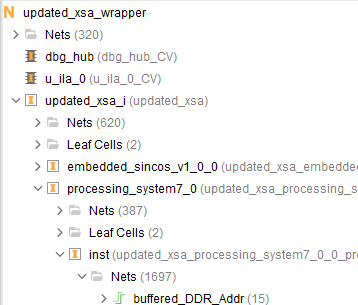

get_debug_cores

dbg_hub u_ila_0

get_property C_USER_SCAN_CHAIN [get_debug_cores dbg_hub]

1