- AMD Community

- Blogs

- Server Processors

- 4th Gen AMD EPYC™ Processors Deliver Superb Perfor...

4th Gen AMD EPYC™ Processors Deliver Superb Performance for Seismic Exploration

- Subscribe to RSS Feed

- Bookmark

- Subscribe

- Printer Friendly Page

- Report Inappropriate Content

What is Seismic Exploration?

Simply put, seismic exploration consists of sending a “shot” of seismic energy into the earth and then recording how that energy bounces off and is refracted by underground features, such as oil and gas reserves. The seismic shot can come from explosives, such as dynamite. However, other techniques, such as air guns, falling weights, or vibration can be used. The shot sends seismic waves into the earth, and a receiving station records the timing and amplitude of the reflected (bounced) and refracted (bent) waves. Elaborate calculations can determine the size, shape, and depth of underground features such as aquifers and oil and gas reservoirs. You can think of seismic exploration as a kind of "x-ray vision" for seeing what lies under the earth.

Seismic surveys are used for a variety of purposes, including scouting landfills, finding underground aquifers, and help predict how a given area will behave during earthquakes--which can help inform building codes that can help save lives. This blog focuses on oil and gas applications because they are among the most used seismic exploration applications.

Testing and Results

AMD performed two series of tests to compare the performance of 4th Gen AMD EPYC processors against both prior 3rd Gen AMD EPYC processors and Intel® Xeon® processors running the Shearwater® Reveal and SLB INTERSECT® seismic exploration applications:

- One series of tests compared 32-core processors to determine how the processors perform on a per-core basis.

- The second series of tests compared top-of-stack processors to determine how the highest-end processors perform on a heads-up basis.

Here’s what this testing revealed:

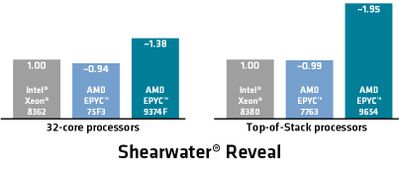

- Shearwater Reveal: Shearwater Reveal is used for time and depth processing and imaging in both land and marine environments. It is primarily licensed to oil and gas companies but is also used to process seismic data for shallow hazard mapping, geothermal projects, carbon capture, deep earth research, water resources, and the nuclear industry. 4th Gen AMD EPYC processors provide strong generational uplifts compared to their 3rd Gen AMD EPYC counterparts. They also demonstrate noticeable performance uplifts compared to the Intel Xeon processors at both 32 cores (~1.38x) and the top of stack (~1.95x). 3rd Gen AMD EPYC processors deliver performance on par with comparable Intel® Xeon® processors in both 32-core and top-of-stack environments, as shown in Figure 1, below.(1)

Figure 1: Relative performance of 3rd and 4th Gen AMD EPYC processors compared to Intel Xeon running Shearwater Reveal

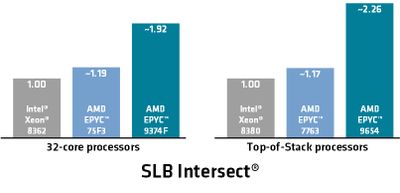

- SLB INTERSECT: SLB INTERSECT is a high-resolution reservoir simulator that combines physics and performance for reservoir models. It offers accurate, efficient field development planning and reservoir management, including black oil waterflood models, thermal SAGD injection schemes, and handling of unstructured grids. 4th Gen AMD EPYC processors deliver excellent generational and competitive performance uplifts compared to both 3rd Gen AMD EPYC processors and Intel Xeon processors. At 32 cores, the AMD EPYC 9374F delivers a performance uplift of ~1.92x compared to the Intel Xeon 8362. At the top of the stack, the 4th Gen AMD EPYC 9564 delivers an impressive uplift of ~2.26x compared to the Intel Xeon 8380. Figure 2 also shows the strong generational uplifts provided by 4th Gen AMD EPYC processors over their 3rd Gen AMD EPYC predecessors at both 32 cores and top of stack.(2)

Figure 2: Relative performance of 3rd and 4th Gen AMD EPYC processors compared to Intel Xeon running SLB Intersect

Takeaways

As I mentioned above, seismic exploration is used for a variety of purposes that can enhance and save lives. In both applications tested, 4th Gen AMD EPYC processors deliver robust generational performance uplifts compared to 3rd Gen AMD EPYC processors at both 32 cores and top of stack. 4th Gen AMD EPYC processors also deliver significant competitive performance uplifts compared to Intel Xeon processors at both 32 cores and top of stack.

Raghu Nambiar is a Corporate Vice President of Data Center Ecosystems and Solutions for AMD. His postings are his own opinions and may not represent AMD’s positions, strategies or opinions. Links to third party sites are provided for convenience and unless explicitly stated, AMD is not responsible for the contents of such linked sites and no endorsement is implied.

References

- For Shearwater Reveal:

- SP5-120, 121: 32-core testing on Shearwater Reveal 5.1-2022-04-27 geophysical software based on AMD measurements as of 10/18/2022. Configurations:

2P AMD EPYC 75F3 (32 cores/socket, 64 cores/node), 1TB Dual-Rank DDR4-3200 memory, Mellanox ConnectX-6 HDR 200Gb InfiniBand x16 PCIe NIC, 1 x 256 GB NVMe OS/ 1 x 1 TB NVMe data, BIOS 1009B, SMT=OFF, Boost=ON, Determinism = performance, Transparent Huge Pages=ON (Default), Swappiness=0, Governor=Performance;

2P AMD EPYC 9374F (32 cores/socket, 64 cores/node); 1.5 TB (24x) Dual-Rank DDR5-4800 64GB DIMMs, 1DIMM per channel; 1 x 256 GB SATA (OS) | 1 x 1 TB NVMe (data); BIOS Version 1002C, SMT=off, Determinism=performance, NPS=4, TDP/ PPT=400;

2P Intel Xeon Platinum 8362 (32 cores/socket, 64 cores/node); 1 TB (16x) Dual-Rank DDR4-3200 64GB DIMMs, 1DIMM per channel; 1 x 256 GB SATA (OS) | 1 x 1 TB NVMe (data); BIOS Version 1.6.5, SMT=off, HPC Profile. Common: RHEL 8.6 OS settings: Clear caches before every run, NUMA balancing 0, randomize_va_space 0. Results may vary due to factors including system configurations, software versions and BIOS settings. - SP5-122, 123: Top-of-stack testing on Shearwater Reveal 5.1-2022-04-27 geophysical software based on AMD measurements as of 10/18/2022. 2P AMD EPYC 7763 (64 cores/socket, 128 cores/node), 1TB Dual-Rank DDR4-3200 memory, Mellanox ConnectX-6 HDR 200Gb InfiniBand x16 PCIe NIC, 1 x 256 GB NVMe OS/ 1 x 1 TB NVMe data, BIOS 1009B, SMT=OFF, Boost=ON, Determinism = performance, Transparent Huge Pages=ON (Default), Swappiness=0, Governor=Performance;

2P AMD EPYC 9654 (96 cores/socket, 192 cores/node); 1.5 TB (24x) Dual-Rank DDR5-4800 64GB DIMMs, 1DIMM per channel; 1 x 256 GB SATA (OS) | 1 x 1 TB NVMe (data); BIOS Version 1001C, SMT=off, Determinism=performance, NPS=4, TDP/ PPT=400 versus;

2P Intel Xeon Platinum 8380 (40 cores/socket, 80 cores/node); 1 TB (16x) Dual-Rank DDR4-3200 64GB DIMMs, 1DIMM per channel; 1 x 256 GB SATA (OS) | 1 x 1 TB NVMe (data); BIOS Version 1.6.5, SMT=off, HPC Profile. Common: RHEL 8.6 OS settings: Clear caches before every run, NUMA balancing 0, randomize_va_space 0. Results may vary due to factors including system configurations, software versions and BIOS settings.

- SP5-120, 121: 32-core testing on Shearwater Reveal 5.1-2022-04-27 geophysical software based on AMD measurements as of 10/18/2022. Configurations:

- For SLB Intersect:

- SP5-124, 125: 32-core testing on SLB Intersect 2021.4 reservoir simulation software (rsim-ix) based on AMD measurements as of 10/18/2022. Configurations:

2P AMD EPYC 75F3, (32 cores/socket, 64 cores/node), 1TB Dual-Rank DDR4-3200 memory, Mellanox ConnectX-6 HDR 200Gb InfiniBand x16 PCIe NIC, 1 x 256 GB NVMe OS/ 1 x 1 TB NVMe data, BIOS 1009B, SMT=OFF, Boost=ON, Determinism = performance, Transparent Huge Pages=ON (Default), Swappiness=0, Governor=Performance

2P AMD EPYC 9374F (32 cores/socket, 64 cores/node); 1.5 TB (24x) Dual-Rank DDR5-4800 64GB DIMMs, 1DIMM per channel; 1 x 256 GB SATA (OS) | 1 x 1 TB NVMe (data); BIOS Version 1002C, SMT=off, Determinism=performance, NPS=4, TDP/ PPT=400;

2P Intel Xeon Platinum 8362 (32 cores/socket, 64 cores/node); 1 TB (16x) Dual-Rank DDR4-3200 64GB DIMMs, 1DIMM per channel; 1 x 256 GB SATA (OS) | 1 x 1 TB NVMe (data); BIOS Version 1.6.5, SMT=off, HPC Profile. Common: RHEL 8.6 OS settings: Clear caches before every run, NUMA balancing 0, randomize_va_space 0. Results may vary due to factors including system configurations, software versions and BIOS settings. - SP5-126, 127: Top-of-stack testing on SLB Intersect 2021.4 reservoir simulation software (rsim-ix) based on AMD measurements as of 10/18/2022. Configurations: 2P AMD EPYC 7763 (64 cores/socket, 128 cores/node); 1TB Dual-Rank DDR4-3200 memory, Mellanox ConnectX-6 HDR 200Gb InfiniBand x16 PCIe NIC, 1 x 256 GB NVMe OS/ 1 x 1 TB NVMe data, BIOS 1009B, SMT=OFF, Boost=ON, Determinism = performance, Transparent Huge Pages=ON (Default), Swappiness=0, Governor=Performance;

2P AMD EPYC 9654 (96 cores/socket, 128 cores/node); 1.5 TB (24x) Dual-Rank DDR5-4800 64GB DIMMs, 1DIMM per channel; 1 x 256 GB SATA (OS) | 1 x 1 TB NVMe (data); BIOS Version 1001C, SMT=off, Determinism=performance, NPS=4, TDP/ PPT=400;

2P Intel Xeon Platinum 8380 (40 cores/socket, 80 cores/node); 1 TB (16x) Dual-Rank DDR4-3200 64GB DIMMs, 1DIMM per channel; 1 x 256 GB SATA (OS) | 1 x 1 TB NVMe (data); BIOS Version 1.6.5, SMT=off, HPC Profile. Common: RHEL 8.6 OS settings: Clear caches before every run, NUMA balancing 0, randomize_va_space 0. Results may vary due to factors including system configurations, software versions and BIOS settings.

- SP5-124, 125: 32-core testing on SLB Intersect 2021.4 reservoir simulation software (rsim-ix) based on AMD measurements as of 10/18/2022. Configurations:

-

AI & Machine Learning

24 -

AMD

1 -

AMD Instinct Accelerators Blog

1 -

Cloud Computing

33 -

Database & Analytics

25 -

EPYC

112 -

EPYC Embedded

1 -

Financial Services

17 -

HCI & Virtualization

28 -

High-Performance Computing

35 -

Instinct

9 -

Supercomputing & Research

8 -

Telco & Networking

13 -

Zen Software Studio

4

- « Previous

- Next »