- AMD Community

- Communities

- PC Processors

- PC Processors

- Understanding Zen3+ UMC channels

PC Processors

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Understanding Zen3+ UMC channels

According to AMD specs "Processor Programming Reference (PPR) for AMD Family 19h Model 11h, Revision B1 Processors", bit 31 "SdpInit" of "SDP Control" register has to be set for each enabled UMC channel. Address 0xN50104 where N is the channel number to probe.

Ryzen 5 6600H is here configured with two 8GB DIMM ref "MTC4C10163S1SC48BA1", thus I'm expecting to read a pair of SDP Control as enabled but not all four registers 0x050104, 0x150104, 0x250104, 0x350104 bit 31 set.

I can guarantee this algorithm is perfectly working on all Zen1 up to Zen4 where for instance only two "SDP Control" have bit 31 set on a Dual Channel setup.

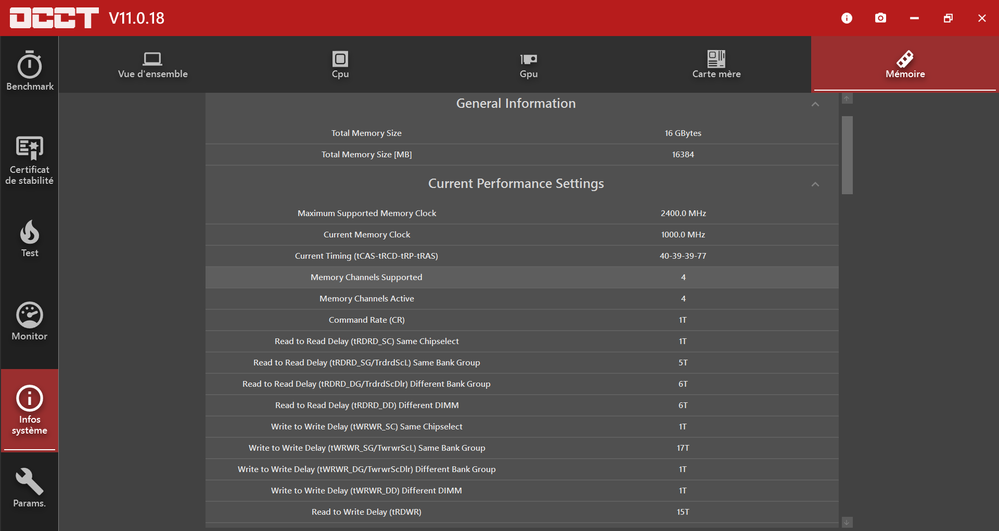

As you can see in screenshot, the Memory Channels Supported but especially Active is four. which is architecturally correct to my understanding of Rembrandt. although I'm still wondering how 4 channels can be with two DIMM installed ?

Not talking about SPD, SMBIOS, DMI or other instrumentation, how I'm suppose to count the number of active channels from the UMC registers queried through SMU ?

Cyril

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In case you don't get many answers to your technical thread try posting this same thread at AMD Developer's Forum.

Start here first to get access to the Developer's forum: https://community.amd.com/t5/newcomers-start-here/bd-p/newcomer-forum

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content